- 您现在的位置:买卖IC网 > Sheet目录1243 > SI5023-EVB (Silicon Laboratories Inc)BOARD EVALUATION FOR SI5023

�� �

�

Si5023-EVB�

�Functional� Description�

�The� evaluation� board� simplifies� characterization� of� the�

�Si5023� Clock� and� Data� Recovery� (CDR)� device� by�

�providing� access� to� all� of� the� Si5023� I/Os.� Device�

�performance� can� be� evaluated� by� following� the� “Test�

�Configuration”� section.� Specific� performance� metrics�

�include� input� sensitivity,� jitter� tolerance,� jitter� generation,�

�and� jitter� transfer.�

�Power� Supply�

�The� evaluation� board� requires� one� 3.3� V� supply.� Supply�

�filtering� is� placed� on� the� board� to� filter� typical� system�

�When� applied,� REFCLK� is� used� to� center� the� frequency�

�of� the� DSPLL?� so� that� the� device� can� lock� to� the� data.�

�Ideally,� the� REFCLK� frequency� should� be� 1/128th,�

�1/32nd,� or� 1/16th� the� VCO� frequency� and� must� have� a�

�frequency� accuracy� of� ±100� ppm.� Internally,� the� CDR�

�automatically� recognizes� the� REFCLK� frequency� within�

�one� of� these� three� frequency� ranges.� Typical� REFCLK�

�frequencies� are� given� in� Table� 1.� REFCLK� is� ac� coupled�

�to� the� SMA� jacks� located� on� the� top� side� of� the�

�evaluation� board.�

�Table� 1.� Typical� REFCLK� Frequencies�

�noise� components;� however,� initial� performance� testing�

�should� use� a� linear� supply� capable� of� supplying� the�

�nominal� voltage� ±5%� dc.�

�CAUTION� :� The� evaluation� board� is� designed� so� that� the�

�body� of� the� SMA� jacks� and� GND� are� shorted.� Care� must�

�be� taken� when� powering� the� PCB� at� potentials� other�

�SONET/SDH�

�19.44� MHz�

�77.76� MHz�

�Gigabit�

�Ethernet�

�19.53� MHz�

�78.125� MHz�

�SONET/SDH�

�with�

�15/14� FEC�

�20.83� MHz�

�83.31� MHz�

�Ratio� of�

�VCO� to�

�REFCLK�

�128�

�32�

�than� GND� at� 0.0� V� and� VDD� at� 3.3� V� relative� to� chassis�

�GND.�

�155.52� MHz� 156.25� MHz� 166.63� MHz�

�16�

�Device� Powerdown�

�The� CDR� can� be� powered� down� via� the� RESET/CAL�

�signal.� When� asserted,� the� evaluation� board� will� draw�

�minimal� current.� RESET/CAL� is� controlled� via� one�

�jumper� located� in� the� lower� left-hand� corner� of� the�

�evaluation� board.� RESET/CAL� is� wired� to� the� signal�

�post� adjacent� to� the� VDD� post.� For� a� valid� reset� to� occur�

�when� using� external� reference� clock� mode,� a� proper�

�external� reference� clock� frequency� must� be� applied� as�

�specified� in� Table� 1.� CLKOUT,� DATAOUT,� DATAIN�

�CLKOUT,� DATAOUT,� and� DATAIN� (all� high-speed� I/Os)�

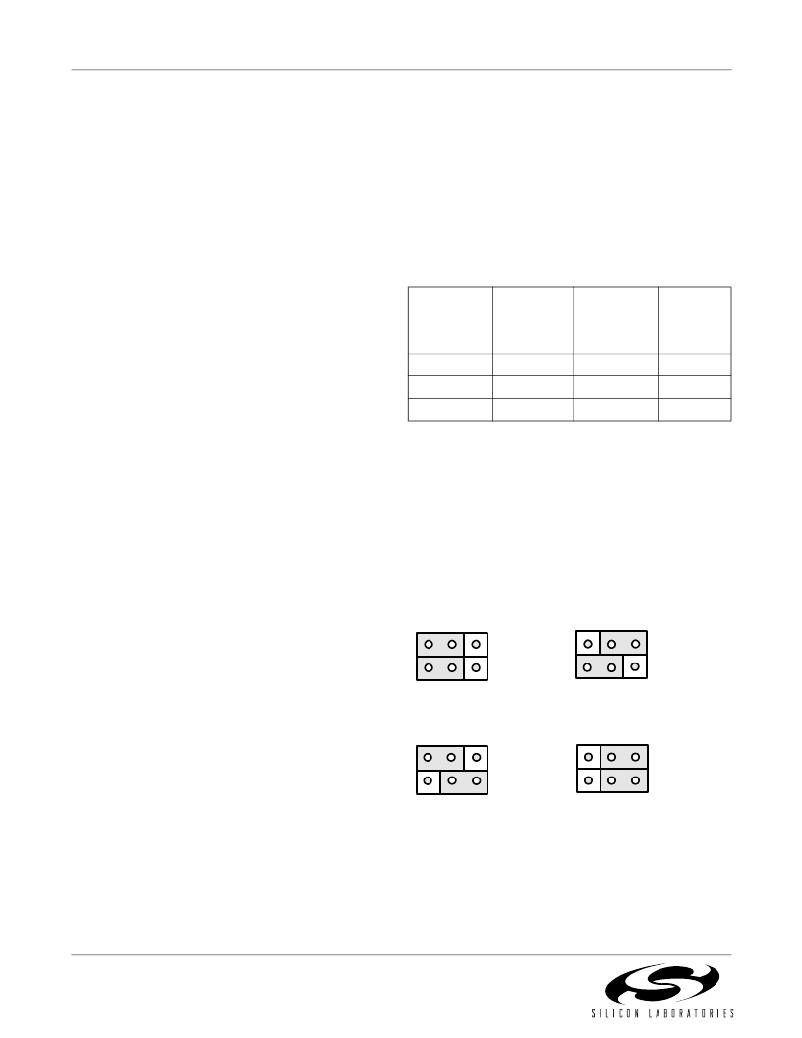

�RATESEL�

�RATESEL� is� used� to� configure� the� CDR� to� recover� clock�

�and� data� at� different� data� rates.� RATESEL� is� a� two� bit�

�binary� input� controlled� via� two� jumpers� located� in� the�

�lower� left-hand� corner� of� the� evaluation� board.�

�RATESEL0/1� are� wired� to� the� center� posts� (signal� post)�

�between� VDD� and� GND.� For� example,� the� OC-48� data�

�rate� is� selected� by� jumping� RATESEL0� to� 1� and�

�RATESEL1� to� 1.�

�are� wired� to� the� board� perimeter� on� 30� mil� (0.030� inch)�

�50� ?� microstrip� lines� to� the� end-launch� SMA� jacks� as�

�labeled� on� the� PCB.� These� I/Os� are� ac� coupled� to�

�simplify� direct� connection� to� a� wide� array� of� standard�

�test� hardware.� Because� each� of� these� signals� are�

�differential,� both� the� positive� (+)� and� negative� (–)�

�terminals� must� be� terminated� to� 50� ?� .� Terminating� only�

�one� side� will� adversely� degrade� the� performance� of� the�

�CDR.� The� inputs� are� terminated� on� the� die� with� 50� ?�

�resistors.�

�Note:� The� 50� ?� termination� is� for� each� terminal/side� of� a� dif-�

�2488� Mbps�

�RATESEL1�

�RATESEL0�

�RATESEL1�

�RATESEL0�

�622� Mbps�

�RATESEL1�

�RATESEL0�

�RATESEL1�

�RATESEL0�

�ferential� signal,� thus� the� differential� termination� is� actu-�

�ally� 50� ?� +� 50� ?� =� 100� ?� .�

�REFCLK�

�REFCLK� is� optional� for� clock� and� data� recovery� within�

�the� Si5023� device.� If� REFCLK� is� not� used,� jumper� both�

�JP15� and� JP16.� These� jumpers� pull� the� REFCLK+� input�

�to� VDD� and� REFCLK–� input� to� GND,� which� configures�

�the� device� to� operate� without� an� external� reference.�

�1244� Mbps� 155� Mbps�

�Figure� 1.� RATESEL� Jumper� Configurations�

�Loss-of-Lock� (LOL)�

�Loss-of-lock� (LOL)� is� an� indicator� of� the� relative�

�frequency� between� the� data� and� the� REFCLK.� LOL� will�

�assert� when� the� frequency� difference� is� greater� than�

�±600� ppm.� In� order� to� prevent� LOL� from� de-asserting�

�2�

�Rev.� 1.1�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SI5110-EVB

BOARD EVALUATION FOR SI5110

SI5320-EVB

BOARD EVALUATION FOR SI5320

SI5321-EVB

BOARD EVALUATION FOR SI5321

SI5364-EVB

BOARD EVALUATION FOR SI5364

SI5XX-PROG-EVB

KIT EVALUATION FOR SI5XX

SI84XXCOM-RD

KIT EVAL FOR SI84XXCOM

SILICON-EXPLORER II

SOFTWARE ANALYSIS EXPLORER LOGIC

SILINKPS-EVB

DAUGHTER CARD PROSLIC PS

相关代理商/技术参数

SI5023-X-GM

制造商:Silicon Laboratories Inc 功能描述:

SI-50242-F

制造商:Bel Fuse 功能描述:- Trays 制造商:BEL STEWART CONNECTOR 功能描述:Bel Stewart, Internal Part #: SI-50242-F 制造商:BEL STEWART CONNECTOR 功能描述:STEWART, INTERNAL PART #: SI-50242-F

SI502-EVB

制造商:SILABS 制造商全称:SILABS 功能描述:USB plug-in board that allows for evaluation of the Si50x family of CMEMS oscillators.

SI503-EVB

制造商:SILABS 制造商全称:SILABS 功能描述:USB plug-in board that allows for evaluation of the Si50x family of CMEMS oscillators.

SI5040

制造商:SILABS 制造商全称:SILABS 功能描述:10 Gbps XFP Transceiver

SI5040-A-GM

功能描述:以太网 IC XFP TRANSCEIVER RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray

SI5040-B-GM

制造商:Silicon Laboratories Inc 功能描述:

SI5040-B-GM R

制造商:Silicon Laboratories Inc 功能描述: